|

C6678 DDR3 PLL DDR3 PLL为DDR3内存控制器生成接口时钟。当退出上电复位时, DDR3 PLL在启用和使用之前在引导配置期间被编程到有效频率。

DDR3 PLL电源通过DDR3 PLL电源引脚(AVDDA2)从外部提供。外部EMI滤波器电路必须添加到所有PLL电源。请参阅第72页“德州仪器公司相关文件”中KeyStone I设备的硬件设计指南为了获得最佳性能,TI建议所有PLL外部组件位于电路板的一侧,无跳线、开关或其他组件展示。为了减少PLL抖动,最大化开关信号迹线和PLL外部之间的间隔部件(C1、C2和EMI滤波器)。

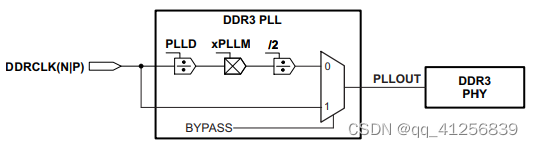

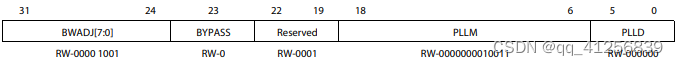

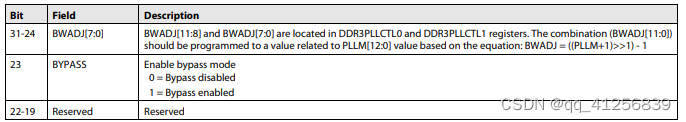

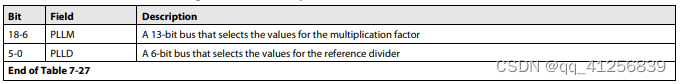

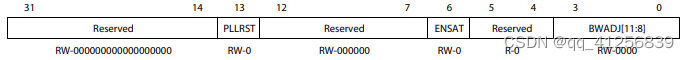

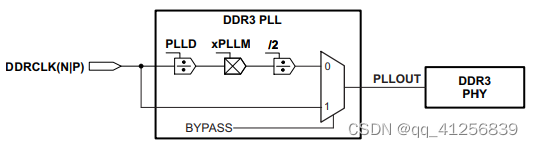

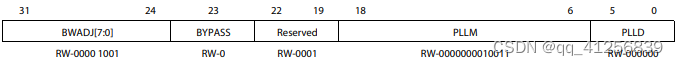

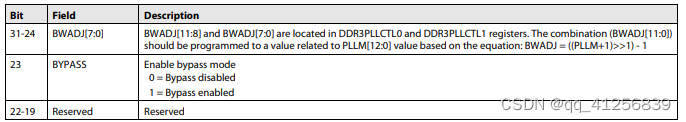

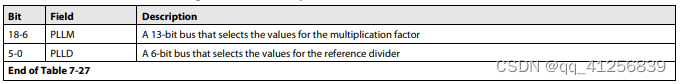

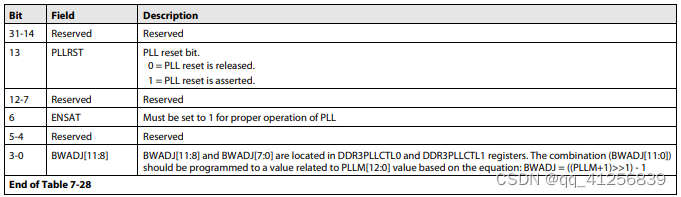

Figure 7-23 shows the DDR3 PLL. Figure 7-23 DDR3 PLL Block Diagram  7.7.1 DDR3 PLL控制寄存器 用于驱动EMIF的DDR PHY的DDR3 PLL不使用PLL控制器。DDR3 PLL可以使用位于Bootcfg模块中的DDR3PLLCTL0和DDR3PLLCTR1寄存器进行控制。这些MMR(内存映射寄存器)存在于Bootcfg空间中。要写入这些寄存器,软件应该经过使用KICK0/KICK1寄存器的解锁序列。有关建议的可配置值,请参阅第83页2.5.4“PLL Boot Configuration Settings”。参阅第80页3.3.4节“Kicker Mechanism Register (KICK0 and KICK1)”,用于寄存器的地址位置以及用于访问寄存器的锁定和解锁序列。此寄存器仅在POR(低电平有效)上复位。 Figure 7-24 DDR3 PLL Control Register 0 (DDR3PLLCTL0)﹙¹﹚ 7.7.1 DDR3 PLL控制寄存器 用于驱动EMIF的DDR PHY的DDR3 PLL不使用PLL控制器。DDR3 PLL可以使用位于Bootcfg模块中的DDR3PLLCTL0和DDR3PLLCTR1寄存器进行控制。这些MMR(内存映射寄存器)存在于Bootcfg空间中。要写入这些寄存器,软件应该经过使用KICK0/KICK1寄存器的解锁序列。有关建议的可配置值,请参阅第83页2.5.4“PLL Boot Configuration Settings”。参阅第80页3.3.4节“Kicker Mechanism Register (KICK0 and KICK1)”,用于寄存器的地址位置以及用于访问寄存器的锁定和解锁序列。此寄存器仅在POR(低电平有效)上复位。 Figure 7-24 DDR3 PLL Control Register 0 (DDR3PLLCTL0)﹙¹﹚  Legend: RW = Read/Write; -n = value after reset 1 This register is reset on POR only. The regreset, reset, and bgreset from PLL are all tied to a common pll0_ctrl_rst_n The pwrdn, regpwrdn, bgpwrdn are all tied to common pll0_ctrl_to_pll_pwrdn. Table 7-27 DDR3 PLL Control Register 0 Field Descriptions (Sheet 1 of 2) Legend: RW = Read/Write; -n = value after reset 1 This register is reset on POR only. The regreset, reset, and bgreset from PLL are all tied to a common pll0_ctrl_rst_n The pwrdn, regpwrdn, bgpwrdn are all tied to common pll0_ctrl_to_pll_pwrdn. Table 7-27 DDR3 PLL Control Register 0 Field Descriptions (Sheet 1 of 2)   Figure 7-25 DDR3 PLL Control Register 1 (DDR3PLLCTL1) Figure 7-25 DDR3 PLL Control Register 1 (DDR3PLLCTL1)

Table 7-28 DDR3 PLL Control Register 1 Field Descriptions Table 7-28 DDR3 PLL Control Register 1 Field Descriptions  7.7.2 DDR3 PLL设备特定信息 如图7-23所示,DDR3 PLL(PLLOUT)的输出除以2,并直接馈送给DDR3存储器控制器。DDR3 PLL受上电复位影响。在上电复位期间,DDR3的内部时钟PLL受到影响,如第133页第7.5节“Reset Controller(复位控制器)”所述。DDR3 PLL仅在在RESETSTAT(低电平有效)引脚变高时锁定。它不会在任何其他重置时解锁。 7.7.2 DDR3 PLL设备特定信息 如图7-23所示,DDR3 PLL(PLLOUT)的输出除以2,并直接馈送给DDR3存储器控制器。DDR3 PLL受上电复位影响。在上电复位期间,DDR3的内部时钟PLL受到影响,如第133页第7.5节“Reset Controller(复位控制器)”所述。DDR3 PLL仅在在RESETSTAT(低电平有效)引脚变高时锁定。它不会在任何其他重置时解锁。

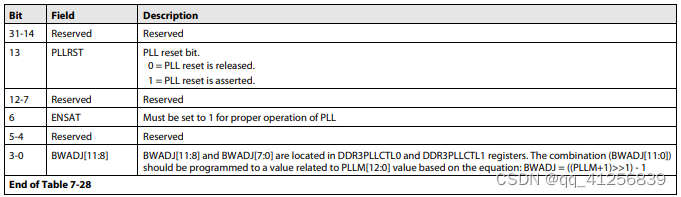

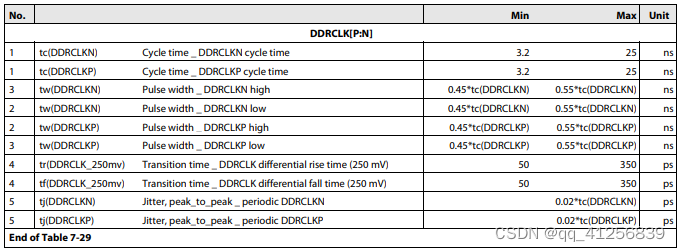

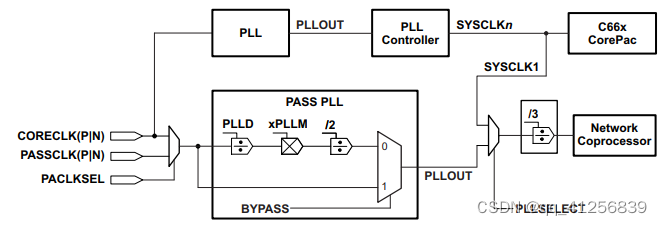

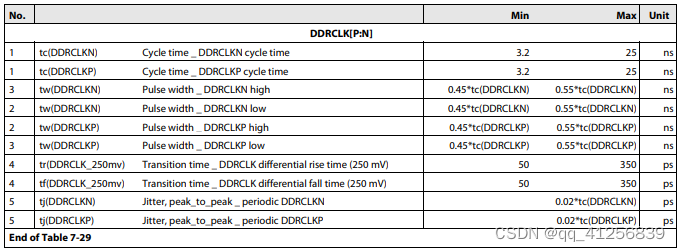

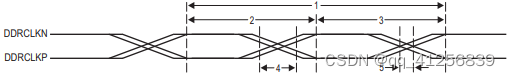

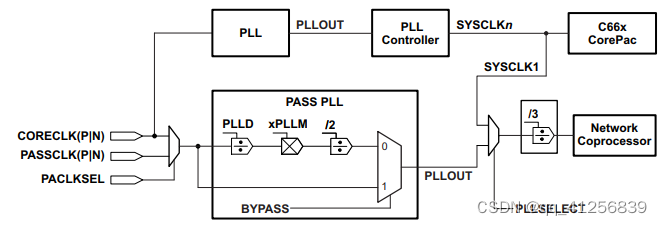

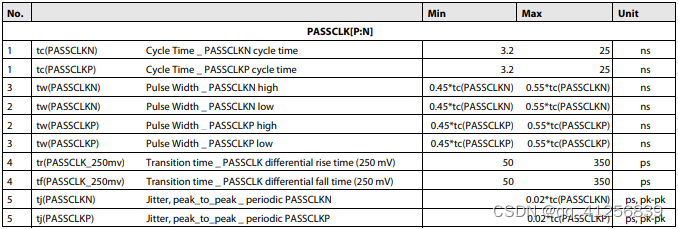

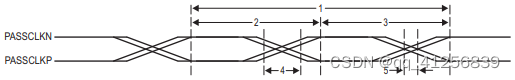

7.7.3 DDR3 PLL初始化序列 请参阅第72页上德克萨斯州“相关文档”中KeyStone设备的锁相环(PLL)用户指南有关DDR3 PLL初始化顺序的详细信息。 ———————————————————————— 注:每次重新编程DDR3 PLL时,DDR3接口必须复位。 ———————————————————————— 7.7.4 DDR3 PLL输入时钟电气数据/定时 Table 7-29 DDR3 PLL DDRSYSCLK1(N|P) Timing Requirements (see Figure 7-26 and Figure 7-22)  Figure 7-26 DDR3 PLL DDRCLK Timing Figure 7-26 DDR3 PLL DDRCLK Timing  7.8 PASS PLL PASS PLL为网络协处理器生成接口时钟。使用PACLKSEL引脚,用户可以选择PASSPLL的输入源作为CORECLK时钟参考源或PASSCLK时钟的输出参考源。当电源关闭复位时,PASS PLL以旁路模式输出,必须在启用和使用之前编程到有效频率。 7.8 PASS PLL PASS PLL为网络协处理器生成接口时钟。使用PACLKSEL引脚,用户可以选择PASSPLL的输入源作为CORECLK时钟参考源或PASSCLK时钟的输出参考源。当电源关闭复位时,PASS PLL以旁路模式输出,必须在启用和使用之前编程到有效频率。

PASSPLL电源通过PASS PLL电源引脚(AVDDA3)提供。外部EMI滤波器电路必须添加到所有PLL电源。请参阅第72页中的“德州仪器相关文档”KeyStone I设备硬件设计指南的详细介绍。为了获得最佳性能,TI建议PLL外部组件位于电路板的一侧,无跳线、开关或其他组件,如图所示。为了减少PLL抖动,最大化开关信号迹线和PLL外部之间的间隔组件(C1、C2和EMI滤波器)。

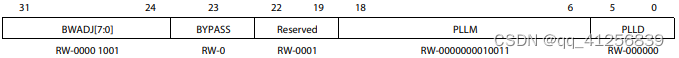

Figure 7-27 shows the PASS PLL. Figure 7-27 PASS PLL Block Diagram  7.8.1 PASS PLL Control Register(PASS PLL控制寄存器) 用于驱动网络协处理器的PASS PLL不使用PLL控制器。PASS PLL可以使用Bootcfg模块中的PASSPLLCTL0和PASSPLLCTL1寄存器进行控制。这些MMR(内存映射寄存器)存在于Bootcfg空间中。要写入这些寄存器,软件应该经过使用KICK0/KICK1寄存器的解锁序列。有关建议的可配置值,请参阅第38页2.5.4“PLL Boot 配置设置”。参见第80页第3.3.4节“‘Kicker Mechanism Register (KICK0 and KICK1)”,用于寄存器的地址位置以及用于访问寄存器的锁定和解锁序列。这个寄存器仅在POR(低电平有效)上复位。 7.8.1 PASS PLL Control Register(PASS PLL控制寄存器) 用于驱动网络协处理器的PASS PLL不使用PLL控制器。PASS PLL可以使用Bootcfg模块中的PASSPLLCTL0和PASSPLLCTL1寄存器进行控制。这些MMR(内存映射寄存器)存在于Bootcfg空间中。要写入这些寄存器,软件应该经过使用KICK0/KICK1寄存器的解锁序列。有关建议的可配置值,请参阅第38页2.5.4“PLL Boot 配置设置”。参见第80页第3.3.4节“‘Kicker Mechanism Register (KICK0 and KICK1)”,用于寄存器的地址位置以及用于访问寄存器的锁定和解锁序列。这个寄存器仅在POR(低电平有效)上复位。

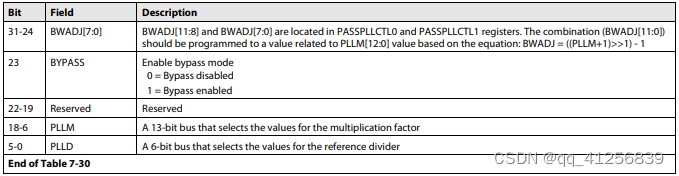

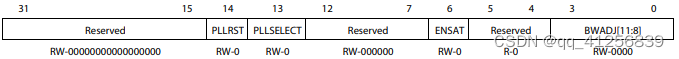

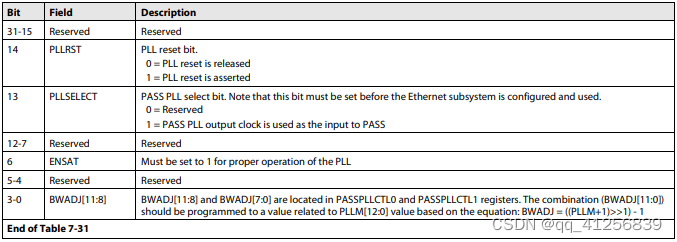

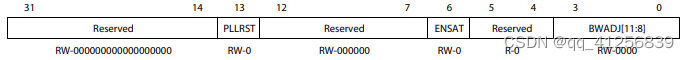

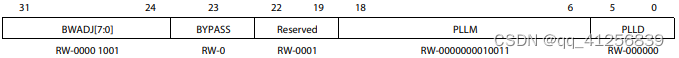

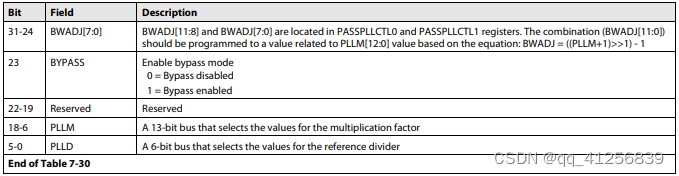

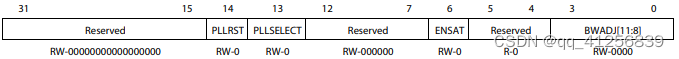

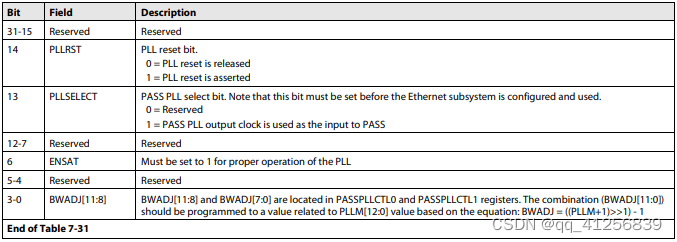

Figure 7-28 PASS PLL Control Register 0 (PASSPLLCTL0)﹙¹﹚  Legend: RW = Read/Write; -n = value after reset 1 This register is Reset on POR only. The regreset, reset and bgreset from PLL are all tied to a common pll0_ctrl_rst_n The pwrdn, regpwrdn, bgpwrdn are all tied to common pll0_ctrl_to_pll_pwrdn. Table 7-30 PASS PLL Control Register 0 Field Descriptions Legend: RW = Read/Write; -n = value after reset 1 This register is Reset on POR only. The regreset, reset and bgreset from PLL are all tied to a common pll0_ctrl_rst_n The pwrdn, regpwrdn, bgpwrdn are all tied to common pll0_ctrl_to_pll_pwrdn. Table 7-30 PASS PLL Control Register 0 Field Descriptions  Figure 7-29 PASS PLL Control Register 1 (PASSPLLCTL1) Figure 7-29 PASS PLL Control Register 1 (PASSPLLCTL1)  Legend: RW = Read/Write; -n = value after reset Table 7-31 PASS PLL Control Register 1 Field Descriptions Legend: RW = Read/Write; -n = value after reset Table 7-31 PASS PLL Control Register 1 Field Descriptions  7.8.2 PASS PLL Device-Specific Information 如图7-27所示,PASS PLL(PLLOUT)的输出除以2,并直接馈送给网络协处理器。PASS PLL受通电复位影响。通电复位期间,PASS的内部时钟PLL受到影响,如第133页第7.5节“重置控制器”所述。PASS PLL仅在并且在RESETSTAT(低电平有效)引脚变高时被锁定。在其它任何复位过程中,它都不会失去锁定。 7.8.3 PASS PLL Initialization Sequence 请参阅“德州仪器相关文档”第72页中KeyStone设备的锁相环(PLL)用户指南有关PASS PLL初始化顺序的详细信息。 7.8.2 PASS PLL Device-Specific Information 如图7-27所示,PASS PLL(PLLOUT)的输出除以2,并直接馈送给网络协处理器。PASS PLL受通电复位影响。通电复位期间,PASS的内部时钟PLL受到影响,如第133页第7.5节“重置控制器”所述。PASS PLL仅在并且在RESETSTAT(低电平有效)引脚变高时被锁定。在其它任何复位过程中,它都不会失去锁定。 7.8.3 PASS PLL Initialization Sequence 请参阅“德州仪器相关文档”第72页中KeyStone设备的锁相环(PLL)用户指南有关PASS PLL初始化顺序的详细信息。

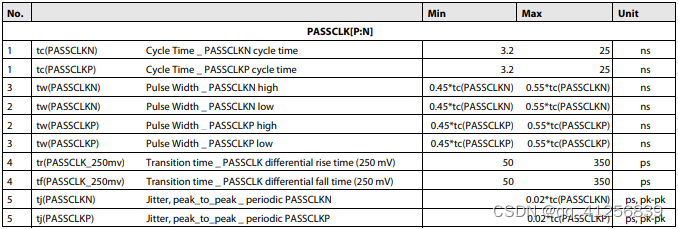

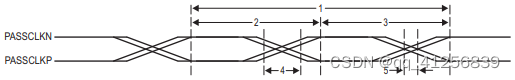

7.8.4 PASS PLL Input Clock Electrical Data/Timing(PASS PLL输入时钟电气数据/定时) Table 7-32 PASS PLL Timing Requirements (See Figure 7-30 and Figure 7-22)  Figure 7-30 PASS PLL Timing Figure 7-30 PASS PLL Timing  注:部分翻译后不清楚是否正确,暂时使用原文档的英文。 注:部分翻译后不清楚是否正确,暂时使用原文档的英文。

|  7.7.1 DDR3 PLL控制寄存器 用于驱动EMIF的DDR PHY的DDR3 PLL不使用PLL控制器。DDR3 PLL可以使用位于Bootcfg模块中的DDR3PLLCTL0和DDR3PLLCTR1寄存器进行控制。这些MMR(内存映射寄存器)存在于Bootcfg空间中。要写入这些寄存器,软件应该经过使用KICK0/KICK1寄存器的解锁序列。有关建议的可配置值,请参阅第83页2.5.4“PLL Boot Configuration Settings”。参阅第80页3.3.4节“Kicker Mechanism Register (KICK0 and KICK1)”,用于寄存器的地址位置以及用于访问寄存器的锁定和解锁序列。此寄存器仅在POR(低电平有效)上复位。 Figure 7-24 DDR3 PLL Control Register 0 (DDR3PLLCTL0)﹙¹﹚

7.7.1 DDR3 PLL控制寄存器 用于驱动EMIF的DDR PHY的DDR3 PLL不使用PLL控制器。DDR3 PLL可以使用位于Bootcfg模块中的DDR3PLLCTL0和DDR3PLLCTR1寄存器进行控制。这些MMR(内存映射寄存器)存在于Bootcfg空间中。要写入这些寄存器,软件应该经过使用KICK0/KICK1寄存器的解锁序列。有关建议的可配置值,请参阅第83页2.5.4“PLL Boot Configuration Settings”。参阅第80页3.3.4节“Kicker Mechanism Register (KICK0 and KICK1)”,用于寄存器的地址位置以及用于访问寄存器的锁定和解锁序列。此寄存器仅在POR(低电平有效)上复位。 Figure 7-24 DDR3 PLL Control Register 0 (DDR3PLLCTL0)﹙¹﹚  Legend: RW = Read/Write; -n = value after reset 1 This register is reset on POR only. The regreset, reset, and bgreset from PLL are all tied to a common pll0_ctrl_rst_n The pwrdn, regpwrdn, bgpwrdn are all tied to common pll0_ctrl_to_pll_pwrdn. Table 7-27 DDR3 PLL Control Register 0 Field Descriptions (Sheet 1 of 2)

Legend: RW = Read/Write; -n = value after reset 1 This register is reset on POR only. The regreset, reset, and bgreset from PLL are all tied to a common pll0_ctrl_rst_n The pwrdn, regpwrdn, bgpwrdn are all tied to common pll0_ctrl_to_pll_pwrdn. Table 7-27 DDR3 PLL Control Register 0 Field Descriptions (Sheet 1 of 2)

Figure 7-25 DDR3 PLL Control Register 1 (DDR3PLLCTL1)

Figure 7-25 DDR3 PLL Control Register 1 (DDR3PLLCTL1) Table 7-28 DDR3 PLL Control Register 1 Field Descriptions

Table 7-28 DDR3 PLL Control Register 1 Field Descriptions  7.7.2 DDR3 PLL设备特定信息 如图7-23所示,DDR3 PLL(PLLOUT)的输出除以2,并直接馈送给DDR3存储器控制器。DDR3 PLL受上电复位影响。在上电复位期间,DDR3的内部时钟PLL受到影响,如第133页第7.5节“Reset Controller(复位控制器)”所述。DDR3 PLL仅在在RESETSTAT(低电平有效)引脚变高时锁定。它不会在任何其他重置时解锁。

7.7.2 DDR3 PLL设备特定信息 如图7-23所示,DDR3 PLL(PLLOUT)的输出除以2,并直接馈送给DDR3存储器控制器。DDR3 PLL受上电复位影响。在上电复位期间,DDR3的内部时钟PLL受到影响,如第133页第7.5节“Reset Controller(复位控制器)”所述。DDR3 PLL仅在在RESETSTAT(低电平有效)引脚变高时锁定。它不会在任何其他重置时解锁。 Figure 7-26 DDR3 PLL DDRCLK Timing

Figure 7-26 DDR3 PLL DDRCLK Timing  7.8 PASS PLL PASS PLL为网络协处理器生成接口时钟。使用PACLKSEL引脚,用户可以选择PASSPLL的输入源作为CORECLK时钟参考源或PASSCLK时钟的输出参考源。当电源关闭复位时,PASS PLL以旁路模式输出,必须在启用和使用之前编程到有效频率。

7.8 PASS PLL PASS PLL为网络协处理器生成接口时钟。使用PACLKSEL引脚,用户可以选择PASSPLL的输入源作为CORECLK时钟参考源或PASSCLK时钟的输出参考源。当电源关闭复位时,PASS PLL以旁路模式输出,必须在启用和使用之前编程到有效频率。 7.8.1 PASS PLL Control Register(PASS PLL控制寄存器) 用于驱动网络协处理器的PASS PLL不使用PLL控制器。PASS PLL可以使用Bootcfg模块中的PASSPLLCTL0和PASSPLLCTL1寄存器进行控制。这些MMR(内存映射寄存器)存在于Bootcfg空间中。要写入这些寄存器,软件应该经过使用KICK0/KICK1寄存器的解锁序列。有关建议的可配置值,请参阅第38页2.5.4“PLL Boot 配置设置”。参见第80页第3.3.4节“‘Kicker Mechanism Register (KICK0 and KICK1)”,用于寄存器的地址位置以及用于访问寄存器的锁定和解锁序列。这个寄存器仅在POR(低电平有效)上复位。

7.8.1 PASS PLL Control Register(PASS PLL控制寄存器) 用于驱动网络协处理器的PASS PLL不使用PLL控制器。PASS PLL可以使用Bootcfg模块中的PASSPLLCTL0和PASSPLLCTL1寄存器进行控制。这些MMR(内存映射寄存器)存在于Bootcfg空间中。要写入这些寄存器,软件应该经过使用KICK0/KICK1寄存器的解锁序列。有关建议的可配置值,请参阅第38页2.5.4“PLL Boot 配置设置”。参见第80页第3.3.4节“‘Kicker Mechanism Register (KICK0 and KICK1)”,用于寄存器的地址位置以及用于访问寄存器的锁定和解锁序列。这个寄存器仅在POR(低电平有效)上复位。 Legend: RW = Read/Write; -n = value after reset 1 This register is Reset on POR only. The regreset, reset and bgreset from PLL are all tied to a common pll0_ctrl_rst_n The pwrdn, regpwrdn, bgpwrdn are all tied to common pll0_ctrl_to_pll_pwrdn. Table 7-30 PASS PLL Control Register 0 Field Descriptions

Legend: RW = Read/Write; -n = value after reset 1 This register is Reset on POR only. The regreset, reset and bgreset from PLL are all tied to a common pll0_ctrl_rst_n The pwrdn, regpwrdn, bgpwrdn are all tied to common pll0_ctrl_to_pll_pwrdn. Table 7-30 PASS PLL Control Register 0 Field Descriptions  Figure 7-29 PASS PLL Control Register 1 (PASSPLLCTL1)

Figure 7-29 PASS PLL Control Register 1 (PASSPLLCTL1)  Legend: RW = Read/Write; -n = value after reset Table 7-31 PASS PLL Control Register 1 Field Descriptions

Legend: RW = Read/Write; -n = value after reset Table 7-31 PASS PLL Control Register 1 Field Descriptions  7.8.2 PASS PLL Device-Specific Information 如图7-27所示,PASS PLL(PLLOUT)的输出除以2,并直接馈送给网络协处理器。PASS PLL受通电复位影响。通电复位期间,PASS的内部时钟PLL受到影响,如第133页第7.5节“重置控制器”所述。PASS PLL仅在并且在RESETSTAT(低电平有效)引脚变高时被锁定。在其它任何复位过程中,它都不会失去锁定。 7.8.3 PASS PLL Initialization Sequence 请参阅“德州仪器相关文档”第72页中KeyStone设备的锁相环(PLL)用户指南有关PASS PLL初始化顺序的详细信息。

7.8.2 PASS PLL Device-Specific Information 如图7-27所示,PASS PLL(PLLOUT)的输出除以2,并直接馈送给网络协处理器。PASS PLL受通电复位影响。通电复位期间,PASS的内部时钟PLL受到影响,如第133页第7.5节“重置控制器”所述。PASS PLL仅在并且在RESETSTAT(低电平有效)引脚变高时被锁定。在其它任何复位过程中,它都不会失去锁定。 7.8.3 PASS PLL Initialization Sequence 请参阅“德州仪器相关文档”第72页中KeyStone设备的锁相环(PLL)用户指南有关PASS PLL初始化顺序的详细信息。 Figure 7-30 PASS PLL Timing

Figure 7-30 PASS PLL Timing  注:部分翻译后不清楚是否正确,暂时使用原文档的英文。

注:部分翻译后不清楚是否正确,暂时使用原文档的英文。